What Is A Test Bench In Verilog A Verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the Verilog hardware description language HDL The purpose of a testbench is to provide a way to simulate the behavior of the design under various conditions inputs and scenarios before actually fabricating the

In a testbench simulation the input combinations and DUT are already mentioned in the test bench Verilog file These inputs act as stimuli on the DUT to produce the output test bench simulation We can apply all input combinations in a testbench using a loop We have an option to choose from four loops in Verilog For example if we have four Writing effective test benches in Verilog is a crucial step in the hardware design and verification process By following best practices and incorporating key components into your test bench you can ensure thorough testing and early detection of potential issues in your digital designs Remember to focus on modularity coverage analysis

What Is A Test Bench In Verilog

What Is A Test Bench In Verilog

http://ceryletech.com/img/demos/it-services/careers/generic-6.jpg

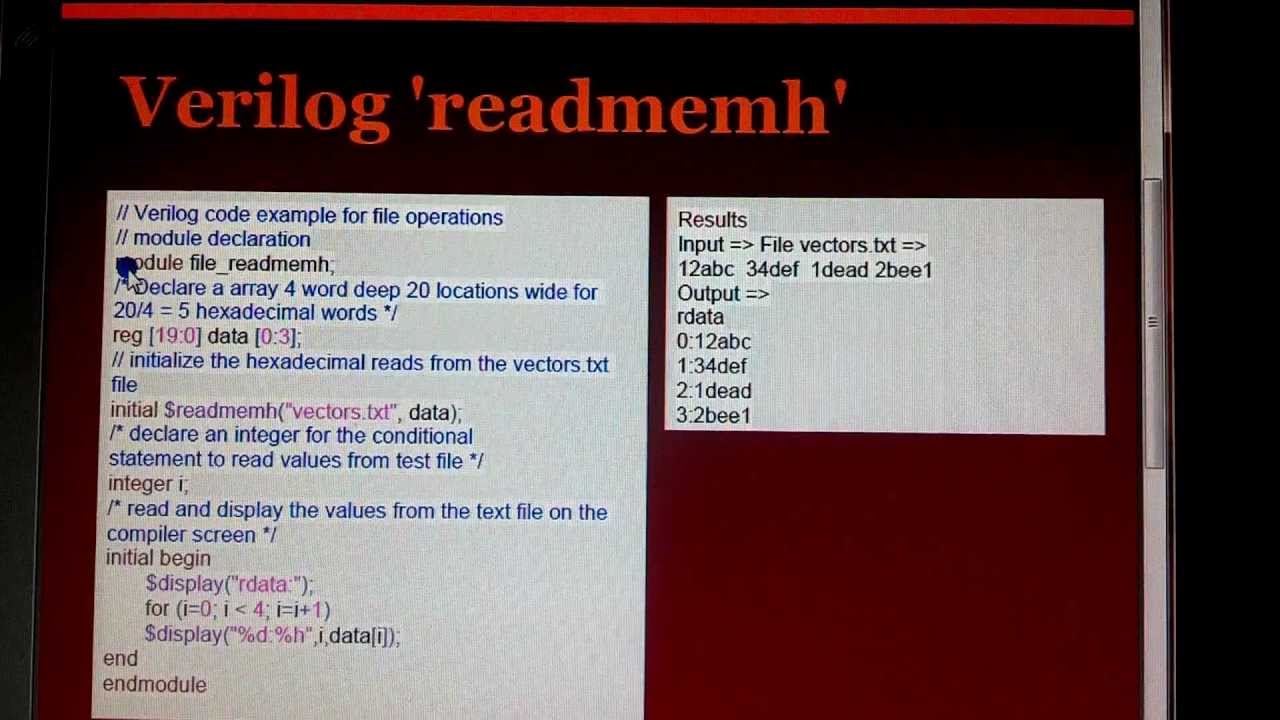

Verilog Test Bench Example Cityjenol

https://cityjenol.weebly.com/uploads/1/3/4/0/134098759/250717532_orig.jpg

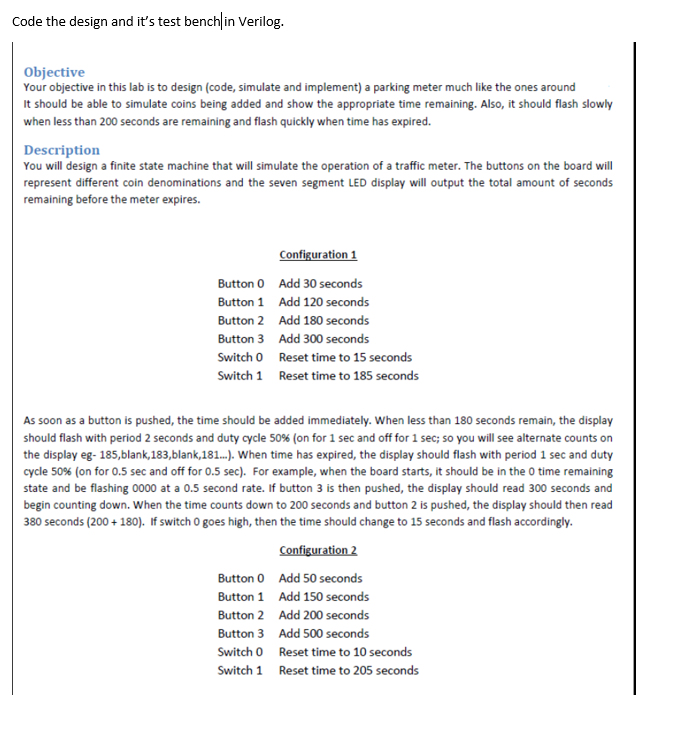

Ode The Design And It s Test Bench In Verilog Chegg

https://d2vlcm61l7u1fs.cloudfront.net/media/b56/b563cfa7-ac5c-45a8-bb97-8584467ba26e/php7vtkSb.png

The testbench is a non synthesizable code that is used only for simulation purposes A typical Verilog testbench consists of the following components DUT instantiation The design under test DUT is instantiated in the testbench The DUT is the module that is being tested Testbench inputs The testbench generates input stimuli to the DUT As a result Verilog starts to look more like a programming or scripting language for testbenches We finally end our testbench with the usual initial block that tells the simulation to run and store the value changes in a particular vcd file

The first step in creating a Verilog test bench is to write the code The test bench code is separate from the DUT code and serves as the environment in which the DUT will be tested It includes the stimulus generation modules result checking modules and any other necessary components To begin we need to define the input and output signals Steps involved in writing a Verilog testbench i Declare a testbench as a module ii Declare set signals that have to be driven to the DUT The signals which are connected to the input of the design can be termed as driving signals whereas the signals which are connected to the output of the design can be termed as monitoring signals

More picture related to What Is A Test Bench In Verilog

Solved Write Verilog Code Not Vhdl Code For Full Adder Using Gate

https://www.coursehero.com/qa/attachment/17338198/

What Is Vhdl In Vlsi Design Talk

https://www.embeddedrelated.com/blogimages/gbreniman/acqeng_list.gif

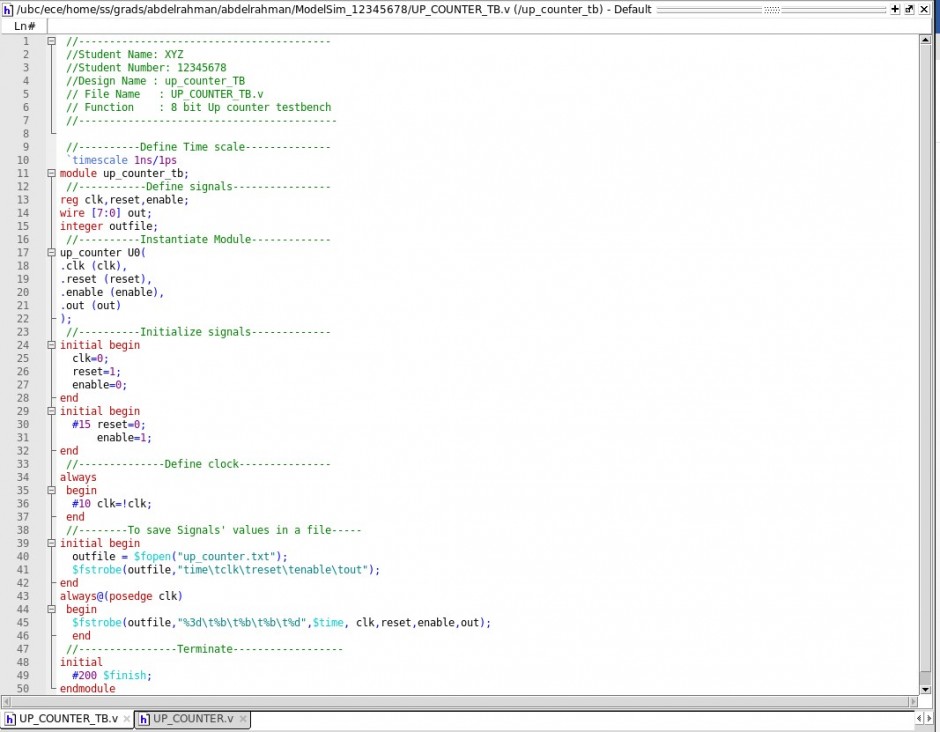

Modelsim Tutorial Verilog Largelalaf

https://sudip.sites.olt.ubc.ca/files/2015/09/6-Verilog-code-for-an-8-Bit-Up-Counter-testbench.-940x732.jpg

Write Testbench First create a test module and note that there should not be any input output ports Because test module generate inputs for top module from inside only So there is no need of input output ports module full adder tb endmodule Instantiate top module inside of the test module module full adder tb Verilog test benches are used for the verification of the digital hardware design Verification is required to ensure the design meets the timing and functionality requirements Verilog Test benches are used to simulate and analyze designs without the need for any physical hardware or any hardware device The most significant advantage of this

A simple testbench will instantiate the Unit Under Test UUT and drive the inputs You should attempt to create all possible input conditions to check every corner case of your project A good testbench should be self checking A self checking testbench is one that can generate inputs and automatically compare actual outputs to expected outputs In Verilog a test bench is a module that is used to simulate and test the functionality of another module or design It provides a set of input stimuli to t

Verilog Code For Half Adder Using Dataflow Modeling BEST GAMES

https://i.ytimg.com/vi/wXx0kr8VMes/maxresdefault.jpg

ESA Test Bench Facility

http://www.esa.int/var/esa/storage/images/esa_multimedia/images/2020/03/test_bench_facility/21907001-1-eng-GB/Test_bench_facility_pillars.jpg

What Is A Test Bench In Verilog - The first step in creating a Verilog test bench is to write the code The test bench code is separate from the DUT code and serves as the environment in which the DUT will be tested It includes the stimulus generation modules result checking modules and any other necessary components To begin we need to define the input and output signals