Test Bench Meaning In Vhdl Q out q 3 Generate Clock and Reset The next thing we do when writing a VHDL testbench is generate a clock and a reset signal We use the after statement to generate the signal concurrently in both instances We generate the clock by scheduling an inversion every 1 ns giving a clock frequency of 1GHz

The simulation process involves compiling the VHDL files and running the simulation The following is an example of a simulation process using ModelSim Launch ModelSim and create a new project Add the VHDL files for the DUT and the testbench to the project Compile the VHDL files by clicking on the Compile button VHDL Testbench is important part of VHDL design to check the functionality of Design through simulation waveform Testbench provide stimulus for design under test DUT or Unit Under Test UUT to check the output result A test bench is HDL code that allows you to provide a documented repeatable set of stimuli that is portable across different

Test Bench Meaning In Vhdl

Test Bench Meaning In Vhdl

https://www.embeddedrelated.com/blogimages/gbreniman/acqeng_list.gif

VHDL Tutorial For OR With Test Bench YouTube

https://i.ytimg.com/vi/a7xuVHNdQNk/maxresdefault.jpg

Vhdl Structural Architecture Electrical Engineering Stack Exchange

https://i.stack.imgur.com/2R7ky.png

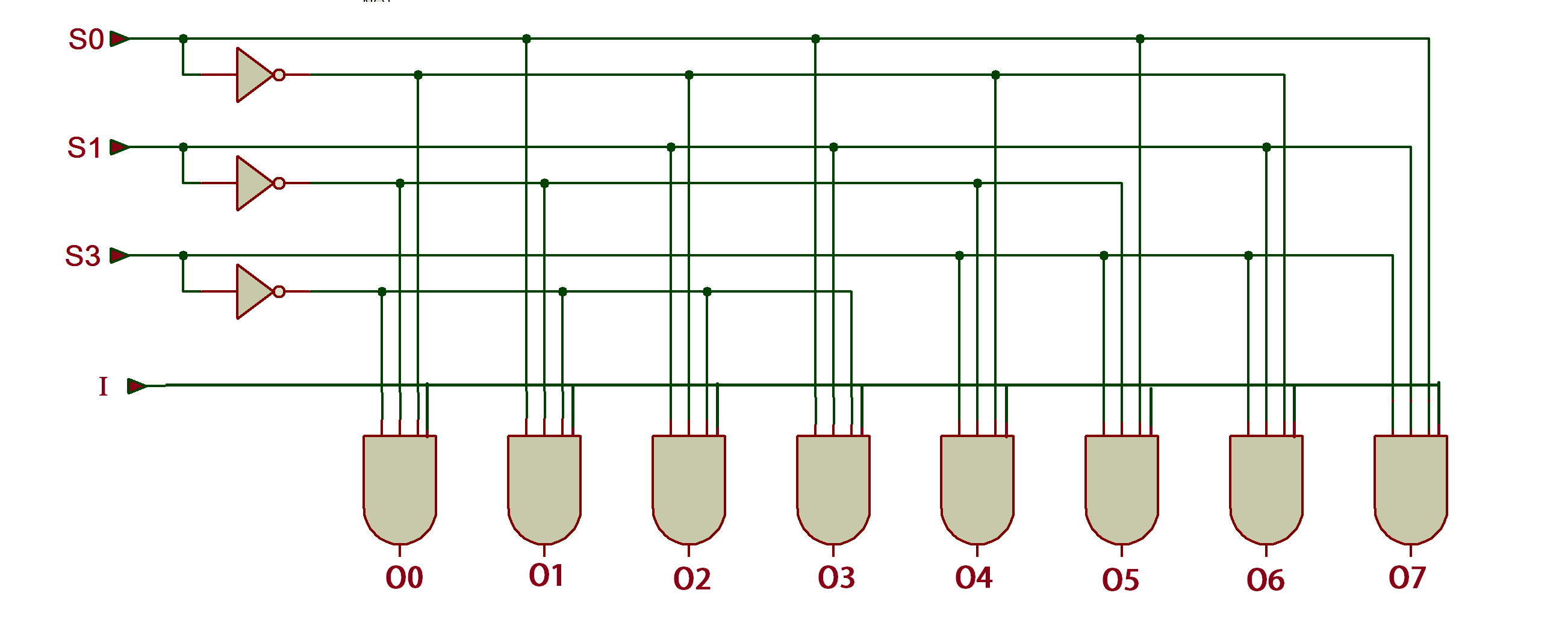

In effect VHDL can be used as a stimulus definition language as well as a hardware description language One consequence of using VHDL to model a test bench is that the test bench is portable between VHDL tools from different vendors Test Bench for MUX4 The entity declaration for a test bench entity TEST MUX4 is end is usually empty VHDL VHDL Testbench is a crucial aspect of digital circuit design It is a simulation environment that allows designers to test their VHDL code before synthesizing it into a hardware device VHDL Testbenches are used to verify the functional correctness of the design identify any potential issues and optimize the design for better performance

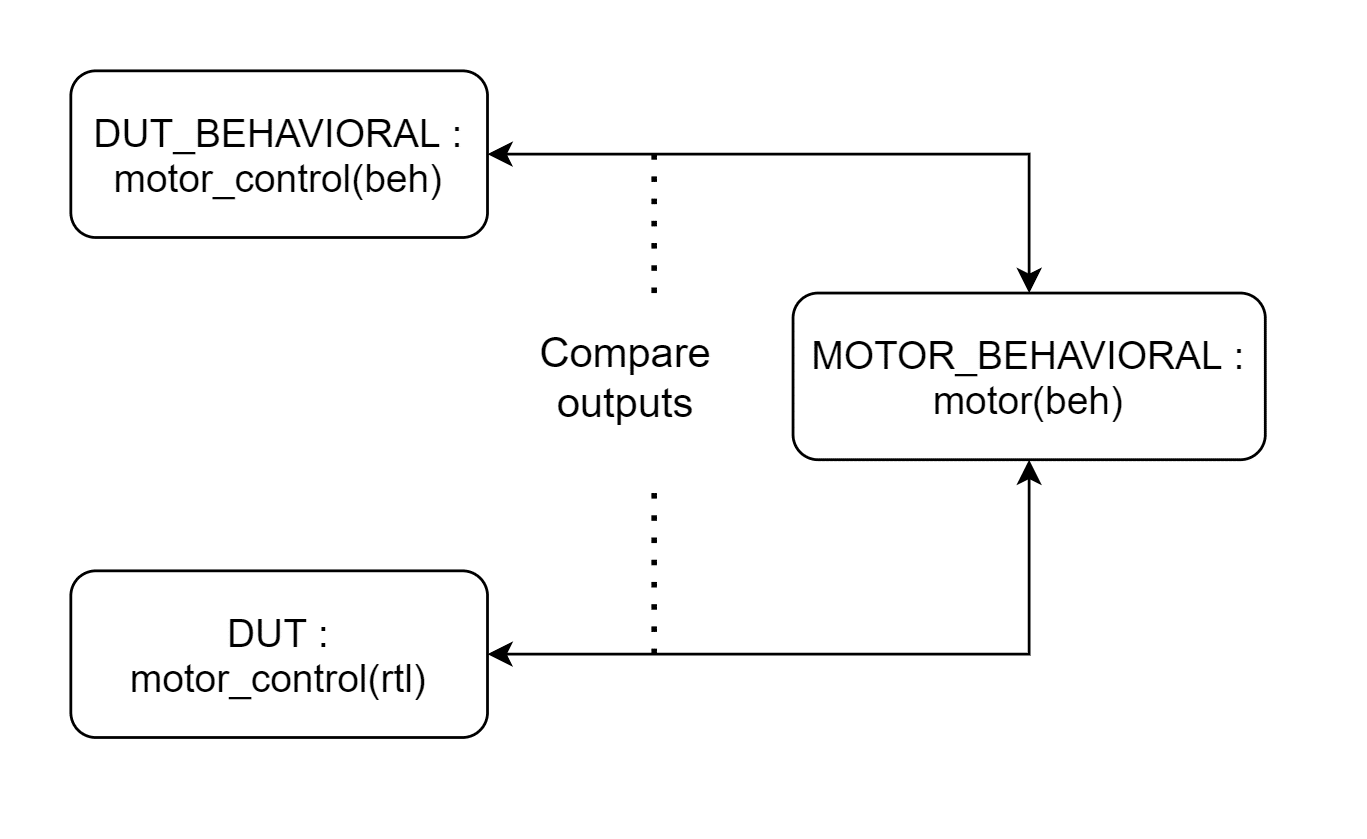

VHDL test bench TB is a piece of code meant to verify the functional correctness of HDL model The main objectives of TB is to Instantiate the design under test DUT Generate stimulus waveforms for DUT Generate reference outputs and compare them with the outputs of DUT Automatically provide a pass or fail indication The VHDL test benches are used for the simulation and verification of FPGA designs The verification is required to ensure that the design meets the timing requirements and is also used to simulate the functionality of the required specifications of the design Testbenches test benches are the primary means of verifications of the HDL designs

More picture related to Test Bench Meaning In Vhdl

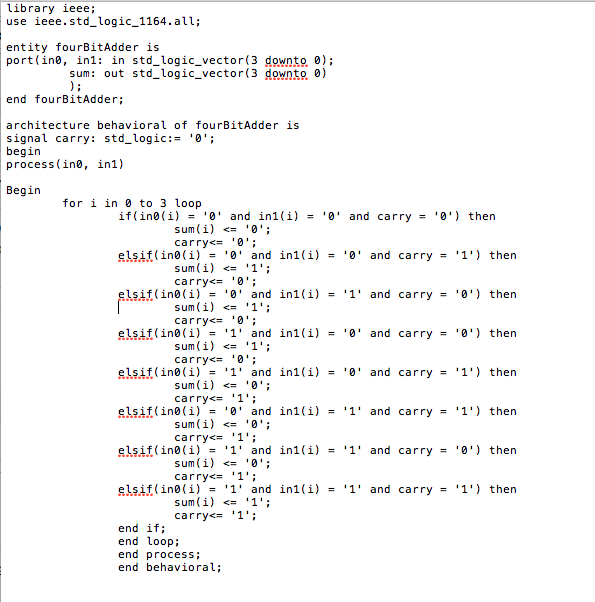

Can Someone Help Me Write A Test Bench In VHDL That Chegg

https://d2vlcm61l7u1fs.cloudfront.net/media/746/746bd5bf-686b-4847-a848-67d85f0e2724/phptfT7Ie.png

Test Bench In Verilog Examples Aaa ai2

https://i.ytimg.com/vi/sGQoBnFcmwc/maxresdefault.jpg

VHDL And FPGA Terminology Combinational Logic

https://cdn.vhdlwhiz.com/wp-content/uploads/2020/09/behavioral-model.png

VHDL Testbench Design Textbook chapters 2 19 4 10 4 12 9 5 The Test Bench Concept Elements of a VHDL Verilog testbench architecture test of adder bench is component adder is declare the adder component port X Y in std logic vector 7 downto 0 VHDL Test Bench Dissected Now is an excellent time to go over the parts of the VHDL test bench A test bench in VHDL consists of same two main parts of a normal VHDL design an entity and architecture The entity is left blank because we are simply supplying inputs and observing the outputs to the design in test The architecture

A self checking testbench is a VHDL program that verifies the correctness of the device under test DUT without relying on an operator to manually inspect the output The self checking testbench runs entirely on its own and prints an OK or Failed message in the end Every VHDL module should have an associated self checking testbench VHDL IN SIMULATION TEST BENCHESBefore processing a design by synthesis tool the designer usually wants to verify that the design perfor s according to the specification This is almost al ays done by running a simulation To simulate the circuit we need to provide not only a design description itself but we need also to write a test bench

VHDL Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using VHDL

https://www.engineersgarage.com/wp-content/uploads/2020/11/demux-ckt.png

VHDL Vs VERILOG Tristate Buffer VHDL With Test Bench

https://2.bp.blogspot.com/-pJGEgqeZJNI/WFuiz0WsI2I/AAAAAAAAAcQ/Z8_h6tEf4h8uNnNrE9FY__d_uztrN5w4gCEw/s1600/Capture1.JPG

Test Bench Meaning In Vhdl - This example shows how to generate a clock and give inputs and assert outputs for every cycle A simple counter is tested here The key idea is that the process blocks run in parallel so the clock is generated in parallel with the inputs and assertions library ieee use ieee std logic 1164 all entity counter tb is